**DDR Output Converter**

Rev A 502446

DF project no: 502446

| Preparation/Review                        | Signature | Date       |

|-------------------------------------------|-----------|------------|

| Author:<br>Alexander Elkiær               | PAE       | 2016-12-22 |

| Check:<br>Christian Nielsen               | CN        | 2016-12-22 |

| Approved by:<br>Christian Glarbo Pedersen | CGPE      | 2016-12-22 |

Revision History Log:

| v i | SIGHT THISCOTY LOS | <i>y</i> • |       |                 |

|-----|--------------------|------------|-------|-----------------|

| ſ   | Date:              | Rev.:      | Init: | Changes:        |

|     | 2016-12-22         | 1          | PAE   | Initial version |

|     |                    |            |       |                 |

|     |                    |            |       |                 |

|     |                    |            |       |                 |

|     |                    |            |       |                 |

# **Reference Documents**

• Schematic 8200093699

# **Abstract**

This document contains the description of the Output Converter for the RSMS-PS.

# Content

|                                                         | Page |

|---------------------------------------------------------|------|

| 1. Introduction                                         | 4    |

| 2. Functional Description                               |      |

| 2.1. Block Schematic                                    |      |

| 2.2. Functional working of Output Converter             |      |

| 3. Interface, signals and plugs/terminals               |      |

| 3.1. X1/X2 High Voltage interface                       |      |

| 3.2. X3 H-Bridge interface                              |      |

| 3.3. X4 Output Terminals                                |      |

| 3.4. X5 DCCT interface                                  |      |

| 3.5. X9 Line Input for FAN                              |      |

| 4. Sub Modules                                          |      |

| 4.1. SIC-MOSFET H-Bridge                                |      |

| 4.2. Gate Drivers                                       |      |

| 4.3. Heat Sink and Fans                                 |      |

| 4.4. Bleeder circuit                                    |      |

| 4.5. Capacitor Storage                                  | 15   |

| 4.6. Over temperature                                   |      |

| 4.7. Earth Leak Detection                               |      |

| 4.8. DCCT for measuring the output current              | 18   |

| 4.9. Output Filter for smooth switch transition and EMC | 19   |

| 5. Mechanic design                                      | 21   |

| 5.1. Output Converter Drawing                           |      |

### 1. Introduction

This document contains description for the detailed design of the Output Converter to be used for the RSMS-PS.

# 2. Functional Description

The Output Converter contains the high power components for the RSMS-PS with supporting circuits. This includes:

- SIC-MOSFET H-Bridge

- Gate drivers

- Bleeder circuit

- Storage capacitors

- Over temperature switch

- Earth leakage detection

- DCCT for measuring the output current

- Heat sink and fans

- Output filters for switch transition control and EMC

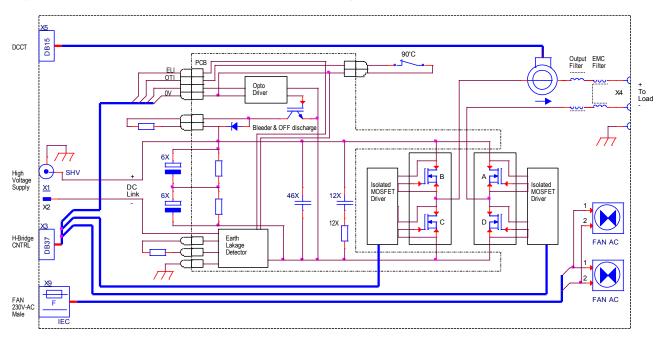

### 2.1. Block Schematic

Figure 1 below shows the block schematic of the Output Converter.

Figure 1

### 2.2. Functional working of Output Converter

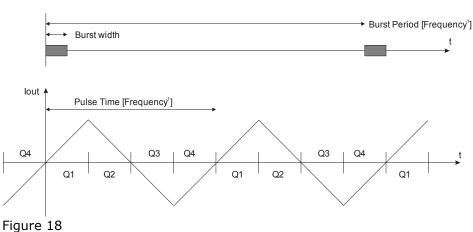

The task of the Output Converter is to convert the DC-link power to the desired triangle shaped load current. The technique for this conversion is described below.

Applying DC voltage to an inductive load, the inductor current will increase given by the formula  $I_L=1/L^*\int V_L^*dt$  where  $I_L$  is the inductor current and  $V_L$  is the voltage across the inductance. With a constant voltage applied across the inductor, the current will change linearly with time (given that the resistive part of the output voltage is much lower than the inductive part). The needed voltage can also be expressed by  $V_L=L_L^*dI_L/dt+R_L^*I_L$  with  $L_L=L_{MAG}+L_{CABLE}$  and  $R_L=R_{MAG}+R_{CABLE}$ .

The above formula shows that a symmetrical square waveform must be applied to the load to achieving a triangle output current shape. This is attained with the H-Bridge output stage.

Due to the relatively high operating frequency (up to 40 kHz), Silicon Carbide MOSFET modules are used in the H-Bridge.

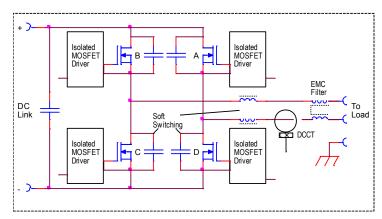

Figure 2 to the right shows the output converter topology.

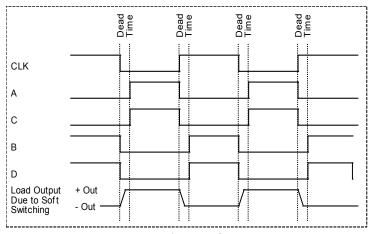

Figure 3 below shows the switching scheme of the H-Bridge. At the top is a perfect square wave. Signals A, B, C and D symbolize the ON state of the H-Bridge quadrants. A small dead time (delay) is added before a given H-Bridge leg is turned ON. During the dead time, where all transistors are OFF, the output filter inductor forms a resonant circuit with the body capacitance of the transistors, helping the switching transition (zero voltage switching).

Figure 2: Output converter topology

Note: The dead time is made large in the figure for clarity.

During a burst, the pulse energy comes from a capacitor bank. Please refer to chapter 4.5 for more information on the capacitor bank.

When the PSU is turned OFF, the capacitor bank will be discharged automatically by an automatic bleeder circuit. For safety, a manual discharge bracket is provided to discharge the capacitor bank during service.

Figure 3: Switch waveforms

# 3. Interface, signals and plugs/terminals

### 3.1. X1/X2 High Voltage interface

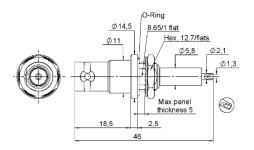

The high voltage is connected with a via an SHV connector on the back of the cabinet. In the coaxial connection, the screen serves as protective earth, and a separate connector is used as return for the charging current. An Amphenol HELIOS H4 connector is foreseen for the return connection.

### X1, SHV Bulkhead Seal Connector

| Pin   | Name | Value | I/O | Description                  |

|-------|------|-------|-----|------------------------------|

| Inner | +HV  | 600V  | I   | Positive High Voltage Supply |

| Outer | PE   | -     | -   | Protective earth             |

Figure 5

Figure 4

#### X2, HELIOS H4 Connector

| Pin | Name   | Value | I/O | Description                |

|-----|--------|-------|-----|----------------------------|

| 1   | HV_RTN | 0V    | I   | High Voltage Supply return |

Figure 7: HELIOS H4 connector, female cable part

Figure 6: HELIOS H4 connector, male panel part

# 3.2. X3 H-Bridge interface

The signals to the H-Bridge Output Converter

DB37 pin Male connector

| Pin | Name            | Value | I/O | Description                                                                                                                                                                                        |

|-----|-----------------|-------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | AD-<br>Power    | 12V   | I   | Power Supply Output Pin for gate driver AD                                                                                                                                                         |

| 20  | AD-<br>Common   |       | -   | Common                                                                                                                                                                                             |

| 2   | AD-<br>HS-P     | 5V    | I   | Positive Line of 5 V Differential High Side PWM Signal Pair. Terminated Into 250 $\Omega$ on gate driver.                                                                                          |

| 21  | AD-<br>HS-N     | 5V    | I   | Negative Line of 5 V Differential High Side PWM Signal Pair. Terminated Into 250 $\Omega$ on gate driver.                                                                                          |

| 3   | AD-<br>LS-P     | 5V    | Ι   | Positive Line of 5 V Differential Low Side PWM Signal Pair. Terminated Into 250 $\Omega$ on gate driver.                                                                                           |

| 22  | AD-<br>LS-N     | 5V    | I   | Negative Line of 5 V Differential Low Side PWM Signal Pair. Terminated Into 250 $\Omega$ on gate driver.                                                                                           |

| 4   | AD-<br>FAULT- P | 5V    | 0   | Positive Line of 5 V Differential Fault Condition Signal Pair.<br>Drive Strength 20 mA.                                                                                                            |

| 23  | AD-<br>FAULT- N | 5V    | 0   | Negative Line of 5 V Differential Fault Condition Signal Pair.<br>Drive Strength 20 mA.                                                                                                            |

| 5   | AD-<br>RTD-P    | 5V    | Ο   | Positive Line of 5 V Temperature Dependent Resistor Output Signal Pair. Drive Strength 20 mA. Temperature Measurement is Encoded Via PWM.                                                          |

| 24  | AD-<br>RTD-N    | 5V    | Ο   | Negative Line of 5 V Temperature Dependent Resistor Output Signal Pair. Drive Strength 20mA. Temperature Measurement is Encoded Via PWM.                                                           |

| 6   | AD-<br>PS-Dis   | 5V    | I   | Pull Down to Disable Power Supply. Pull Up, or Leave Floating to Enable. Gate-Source will be Connected with 10 $k\Omega$ when disabled.                                                            |

| 25  | AD-<br>Common   |       | -   | Common                                                                                                                                                                                             |

| 7   | AD-<br>PWM-EN   | 5V    | I   | Pull Down to Disable PWM Input Logic. Pull Up/Leave floating to enable. Gate-source will be held low through gate resistor if power supplies are enabled.                                          |

| 26  | AD-<br>Common   |       | -   | Common                                                                                                                                                                                             |

| 8   | AD-<br>OC-EN    | 5V    | I   | Over-current Protection Enable. Pull down to disable detection of over-current fault. PWM and UVLO will continue to function. Pull up or leave floating to enable detection of over-current fault. |

| 27  | AD-<br>Common   |       | -   | Common                                                                                                                                                                                             |

| 9   | BC-<br>Power    | 12V   | I   | Power Supply Input Pin for gate driver AD                                                                                                                                                          |

| 28  | BC-<br>Common   |       | -   | Common                                                                                                                                                                                             |

# DB37 pin Male connector

|     |                 |       |     | ·                                                                                                                                                                                                  |

|-----|-----------------|-------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin | Name            | Value | I/O | Description                                                                                                                                                                                        |

| 10  | BC-<br>HS-P     | 5V    | I   | Positive Line of 5 V Differential High Side PWM Signal Pair. Terminated into 250 $\Omega$ on gate driver.                                                                                          |

| 29  | BC-<br>HS-N     | 5V    | I   | Negative Line of 5 V Differential High Side PWM Signal Pair. Terminated into 250 $\Omega$ on gate driver.                                                                                          |

| 11  | BC-<br>LS-P     | 5V    | I   | Positive Line of 5 V Differential Low Side PWM Signal Pair. Terminated into 250 $\Omega$ on gate driver.                                                                                           |

| 30  | BC-<br>LS-N     | 5V    | I   | Negative Line of 5 V Differential Low Side PWM Signal Pair. Terminated into 250 $\Omega$ on gate driver.                                                                                           |

| 12  | BC-<br>FAULT- P | 5V    | 0   | Positive Line of 5 V Differential Fault Condition Signal Pair.<br>Drive Strength 20 mA.                                                                                                            |

| 31  | BC-<br>FAULT- N | 5V    | Ο   | Negative Line of 5 V Differential Fault Condition Signal Pair.<br>Drive Strength 20 mA.                                                                                                            |

| 13  | BC-             | 5V    | 0   | Positive Line of 5 V Temperature Dependent Resistor Output                                                                                                                                         |

|     | RTD-P           |       |     | Signal Pair. Drive Strength 20 mA. Temperature Measurement is Encoded Via PWM.                                                                                                                     |

| 32  | BC-<br>RTD-N    | 5V    | Ο   | Negative Line of 5 V Temperature Dependent Resistor Output Signal Pair. Drive Strength 20mA. Temperature Measurement is Encoded Via PWM.                                                           |

| 14  | BC-<br>PS-Dis   | 5V    | I   | Pull Down to Disable Power Supply. Pull Up, or Leave Floating to Enable. Gate-Source will be Connected with 10 $k\Omega$ when disabled.                                                            |

| 33  | BC-<br>Common   |       | -   | Common                                                                                                                                                                                             |

| 15  | BC-<br>PWM-EN   | 5V    | Ι   | Pull Down to Disable PWM Input Logic. Pull Up/Leave floating to enable. Gate-source will be held low through gate resistor if power supplies are enabled.                                          |

| 34  | BC-<br>Common   |       | _   | Common                                                                                                                                                                                             |

| 16  | BC-<br>OC-EN    | 5V    | Ι   | Over-current Protection Enable. Pull down to disable detection of over-current fault. PWM and UVLO will continue to function. Pull up or leave floating to enable detection of over-current fault. |

| 35  | BC-<br>Common   |       | -   | Common                                                                                                                                                                                             |

| 17  | Power           | 12V   | I   | Power Supply Input Pin                                                                                                                                                                             |

| 36  | CRB-P           | 5V    | I   | Bleeder disable                                                                                                                                                                                    |

| 18  | CRB-N           | 0V    | -   | Return signal for Bleeder disable                                                                                                                                                                  |

| 37  | OTI             | NC    | 0   | Over temperature Interlock (0V as return)                                                                                                                                                          |

| 19  | ELI             | NC    | 0   | Earth Leakage Interlock (0V as return)                                                                                                                                                             |

### 3.3. X4 Output Terminals

The output terminals located at the rear of the Output Converter cabinet has multiple screw connections suited for the multi conductor cables. An angled, panel feed-through terminal block type is foreseen, allowing easy output cable connection from below. Below the output terminals, saddle clamps provide mechanical relief and terminates the screens of the output cables to the output converter cabinet (chassis/ground).

Figure 8: Output cable screw terminals

Figure 9: Output cable saddle clamp

### 3.4. X5 DCCT interface

The signals are connected with a DB15 Male connector on the back of the cabinet.

Pin Name Value I/O **Description** 1 Not connected 2 Resistor to ground OCP-RTN 0 Over Current / Malfunction Return 3 4 0V 0C Common & screen 5 -VCC -15V Ι **Negative Power Supply** 9 0 +Out Proportional output current 1:2000 10 Not connected OCP 0 11 Over Current / Malfunction 12 +VCC +15V Ι Positive Power Supply

**DB15 Male connector**

Non used pins are not connected

## 3.5. X9 Line Input for FAN

The fan power to the Output Converter is passed through an IEC socket.

### Sub Modules

Below is a short description of the modules used.

#### 4.1. SIC-MOSFET H-Bridge

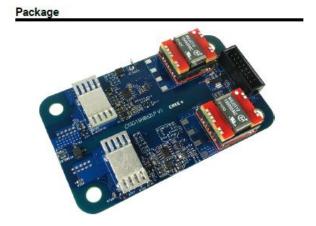

For the output H-Bridge silicon carbide MOSFET type CAS325M12HM2 from the company CREE are foreseen. See datasheet below.

Package

# CREE 🕏

### CAS325M12HM2

1.2kV, 3.6 mΩ All-Silicon Carbide High Performance, Half-Bridge Module C2M MOSFET and Z-Rec™ Diode

| 1.2 kV |

|--------|

| 9.3 mJ |

| 3.6 mΩ |

|        |

65mm x 110mm x 10mm

#### Features

- Ultra Low Loss, Low (5 nH) Inductance

- **Ultra-Fast Switching Operation**

- Zero Reverse Recovery Current from Diode

- Zero Turn-off Tail Current from MOSFET

- Normally-off, Fail-safe Device Operation

- AlSiC Baseplate and Si3N4 AMB Substrate

- Ease of Paralleling

- High Temperature Packaging, T<sub>J(max)</sub> = 175 °C

- AS9100 / ISO9001 Certified Manufacturing

#### System Benefits

- Enables Compact, Lightweight Systems

- **High Efficiency Operation**

- Reduced Thermal Requirements

- Reduced System Cost

#### **Applications**

- High-Efficiency Converters / Inverters

- Motor & Traction Drives

- Smart-Grid / Grid-Tied Distributed Generation

| 600000000000000000000000000000000000000 |

|-----------------------------------------|

|-----------------------------------------|

| Part Number  | Package            | Marking      |

|--------------|--------------------|--------------|

| CAS325M12HM2 | Half-Bridge Module | CAS325M12HM2 |

Figure 10: Section of MOSFET datasheet

The current capability of these devices are given in Table 2.

The applied peak current is 340A and the average current is  $340/\sqrt{3*5.8\%}=11.4A$ , this gives a peak power loss of 429W and an average power loss of 25W, which again results in a case temperature of 58°C with

| continuous | 444A | $@ T_C = 25 °C / T_J = 175 °C$ |

|------------|------|--------------------------------|

| continuous | 350A | $@ T_C = 75 °C / T_J = 175 °C$ |

| Peak       | 500A | @ T <sub>J</sub> = 175°C       |

Table 1

the proposed heatsink (please refer to section 4.3). The MOSFET modules junction temperature is calculated to 71°C, which is a sufficiently safety margin to guarantee high MTBF.

### 4.2. Gate Drivers

As MOSFET driver, the dedicated driver for the chosen MOSFET will be used, see Figure 11 below.

### CGD15HB62LP

#### **Dual Channel Isolated Gate Driver**

Cree CAS325M12HM2 C2M SiC Half Bridge Module Optimized

| V <sub>Drive</sub> | +20/-5 V |

|--------------------|----------|

| l <sub>G</sub>     | ±14 A    |

| R <sub>G</sub>     | 5 Ω      |

#### eatures

- Optimized for Cree's High Performance CAS325M12HM2 Half Bridge Power Modules

- High-Frequency, Ultra-Fast Switching Operation

- . On Board 3 W or 6 W Isolated Power Supplies

- Configurable UVLO with Hysteresis

- Direct Mount Low Inductance Design

- On-Board Overcurrent, Overlap, and Reverse Polarity Protection

#### For Use with Cree Module

CAS325M12HM2, 1200 V, 325 A Module Half Bridge CPM2 Variants for Module Junction Temperatures up to 150 °C

#### Applications

DC Bus Voltages up to 1000 V

| Part Number | Package | Marking        |  |  |

|-------------|---------|----------------|--|--|

| CGD15HB62LP | PCBA    | CGD15HB62LP V1 |  |  |

Figure 11: SiC MOSFET driver

### 4.3. Heat Sink and Fans

A forced air cooled heat sink will be used to cool the H-Bridge MOSFET modules. Besides the MOSFET modules, the bleeder resistor, earth leakage resistor and output filter toroids will also be mounted on the heat sink, each dissipating:

MOSFET modules: 100W (summed average power when operating at full current)

Bleeder resistor: 518W (peak, and only when bleeding)

Earth leakage resistor: 163W (peak, worst case, short-time overload)

Output filter toroids: 5W (summed average power when operating at full current)

Total power to be dissipated 105W (operating at full current, steady state)

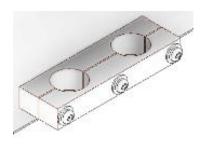

Below is a figure of the heat sink to be used:

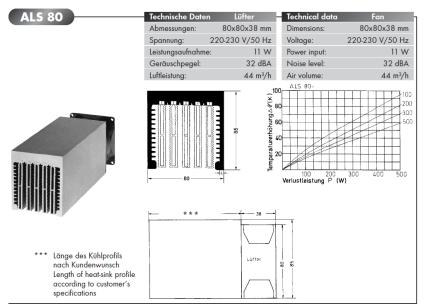

Figure 12: Considered heat sink for the output converter components

The heatsink will make up the full depth of the output converter cabinet, resulting in direct exhaust through the back side of the cabinet.

An extra fan will provide forced exchange of air to ensure cooling of the remaining output converter.

Both fans provide air flow front-to-back, are long-life AC types and are only activated when the power supply is ON.

#### 4.4. Bleeder circuit

Since the capacitor charge PS is a single quadrant power supply (only able to charge, not discharge, the capacitors), a bleeder circuit is implemented in the output converter.

The bleeder allows faster transition when changing output current from a higher set-point to a lower set-point, and provides safety discharge when the power supply is turned OFF.

To reduce power consumption, the bleeder is switched, only bleeding when it has to. That is; when main power is OFF or when the capacitor voltage is more than 2% above required.

For safety, the bleeder will be enabled and bleeding by default, and an active "bleeder disable" signal is required to disable the bleeder. The logic is therefore inversed; the bleeder is disabled when main power is ON and the capacitor voltage is more than 2% below required.

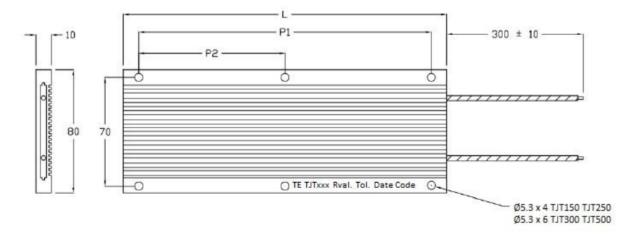

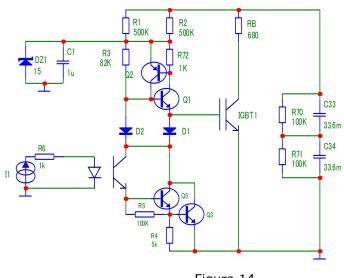

The bleeder circuit consist of a  $680\Omega$  / 500W resistor and two IGBT switches (operated in parallel for redundancy).

When voltage is present on the capacitor bank, the IGBTs are turned on via pull-up resistors (thereby bleeding by default). The bleeder is disabled by the "bleeder disable" signal generated on the Regulation Module (in the Control Crate), driving opto couplers in the IGBT gate drive (pulling the gates down, switching the IGBTs off, disabling the bleeder). The pull-up/opto-coupler circuits will be amplified to allow faster switching and reduce power dissipation in the IGBTs.

| Series | Power<br>rating on<br>Std Heat<br>sink (W) | Power<br>rating in<br>free air<br>(W) | Resistance<br>Range | Dielectric<br>Strength | Standard<br>Chassis |   | L max | P1  | P2<br>_       |

|--------|--------------------------------------------|---------------------------------------|---------------------|------------------------|---------------------|---|-------|-----|---------------|

| TJT150 | 150                                        | 75                                    | 1R0 - 1K0           | 1500                   | 930                 | 3 | 120   | 100 | N/A _         |

| TJT250 | 250                                        | 125                                   | 1R0 - 1K5           | 1500                   | 930                 | 3 | 180   | 160 | N/A _         |

| TJT300 | 300                                        | 150                                   | 1R0 – 1K7           | 1500                   | 1600                | 3 | 210   | 190 | 85 _          |

| TJT500 | 500                                        | 250                                   | 1R0 – 3K0           | 1500                   | 1600                | 3 | 330   | 310 | <b>1</b> 55 _ |

Figure 13

From data sheet, the resistor can withstand 5x rated voltage for 5 seconds or  $5^2 = 25$  times the power.

Under normal condition the power dissipation is 518W within 1.29 seconds going from 100% to 90% output current. The time constant when discharging is 12.2 seconds.

Discharging from full voltage down below 50V safety limit is done within 31 seconds.

On multiple errors (even the maximum output voltage clamp) the peak voltage can rise up to 1kV (output range of capacitor charging PS). In this situation the peak power will be 1500W, which is only 3 times the rated and well below the 25 times stated peak power.

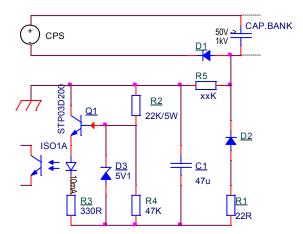

Figure 14 Shows the bleeder circuit

Figure 14

As IGBT, the type IGW08T120 from the company Infineon is chosen. See data sheet below.

In normal condition the total discharge current is below 1A and the IGBT is rated for 8A.

# IGW08T120

### TrenchStop® Series

### Low Loss IGBT in TrenchStop® and Fieldstop technology

- Short circuit withstand time 10μs

- · Designed for :

- Frequency Converters

- Uninterrupted Power Supply

- TrenchStop® and Fieldstop technology for 1200 V applications offers:

- very tight parameter distribution

- high ruggedness, temperature stable behavior

- NPT technology offers easy parallel switching capability due to positive temperature coefficient in V<sub>CE(sat)</sub>

- Low EMI

- Low Gate Charge

- Qualified according to JEDEC¹ for target applications

- Pb-free lead plating; RoHS compliant

- Complete product spectrum and PSpice Models: <a href="http://www.infineon.com/igbt/">http://www.infineon.com/igbt/</a>

| Туре      | V <sub>CE</sub> | I <sub>c</sub> | V <sub>CE(sat), Tj=25°C</sub> | $T_{\rm J,max}$ | Marking Code | Package     |

|-----------|-----------------|----------------|-------------------------------|-----------------|--------------|-------------|

| IGW08T120 | 1200V           | 8A             | 1.7V                          | 150°C           | G08T120      | PG-TO-247-3 |

Figure 15

### 4.5. Capacitor Storage

The energy used in one burst is taken from a capacitor bank. This capacitor bank must be large enough, and have sufficiently low output impedance, to provide the required voltage with the required stability throughout one burst period. To achieve this, the capacitor bank is divided in two parts; one for the high frequency (40kHz) pulsing, and one for the low frequency burst energy occurring at 14 Hz.

#### To high frequency capacitor bank

The total energy to the load is derived from the high frequency capacitor bank in the time slots Q1 and Q3 (see Figure 18) and delivered back in time slots Q2 and Q4.

Ensuring the capability to deliver the high frequency components in a pulse (including switching transitions) and to avoid oscillation problems, an ultra-low parasitic inductance is required. This for both the capacitor bank itself and for the connection to SIC-MOSFETs.

The high frequency capacitor bank is made up of 46 paralleled  $25\mu F/1100V$  power film capacitors each having an ESL of only 35nH.

Calculations data for the high frequency capacitor bank

- Capacitor bank self-inductance = 35/46=0.76nH

+ <2nH for the MOSFET connection

- Capacitor bank ripple current RMS =  $340/\sqrt{3} = 196 (4.27A/Cap)$

(Capacitor rating IRMS = 16.5A)

High frequency DC-Link voltage ripple = 1.3V P-P @ 40kHz (≤ 2‰)

#### Benefits

- Self-healing

- · Low losses

- · High ripple current

- High capacitance density

- High contact reliability

- · Suitable for high frequency applications

Figure 16

To maintain minimal parasitic inductance, the film capacitors are mounted on four-layer printed circuit boards (PCBs) acting as low-inductance laminated busbars from the capacitors to the SIC-MOSFETs. One PCB, located in the bottom of the cabinet, holds the majority of the film capacitors, and a second PCB with additional capacitors connects the high frequency capacitor bank directly to the SIC-MOSFETs.

High frequency resonances between the resulting stray inductance of the capacitors, the small stray inductance and the capacitance of the PCB itself will be dampened by surface mounted R/C circuits located on the PCB directly on top of the SIC-MOSFETs.

### To low frequency capacitor bank

The low frequency capacitor bank is made out of electrolytic capacitors. 6 parallel branches, each consisting of two  $5600\mu\text{F}/500\text{V}$  capacitors in series, are foreseen.

Calculation data for the Low frequency capacitor bank:

- Capacitor bank capacitance = 16.8mF

Capacitor bank ripple current RMS = ≤7A

- (Cap rating IRMS = 15A)

- Low frequency DC-Link voltage ripple =  $3V P-P @ 14Hz (\le 5\%)$

PG - 6DI

Figure 17

### 4.6. Over temperature

In normal operation the heat sink is calculated to be 13°C above ambient temperature.

A normally closed thermal switch (operating at 75°C) will monitor the temperature on the heat sink. When activated, an interlock will be generated, switching the power supply OFF.

#### 4.7. Earth Leak Detection

If an earth leakage or short circuit to ground occurs on the output terminals of the power supply, an earth leak detector circuit will detect the fault and generate an interlock turning the power supply OFF.

As both output terminals jump  $\pm 600V$  when the power supply is bursting, the negative rail of the DC-link is used as the reference point for the earth leakage detection.

To protect the MOSFETs from excessive over-current in case of a short circuit to ground, a soft earth connection is implemented through R2 and R4 (resistive connection).

Figure 19

The capacitor charging power supply ("CPS" in Figure 19) has floating output terminals, but the return signal is only allowed to float <60V with respect to earth. In normal operation, it charges the capacitor bank through D1, and the negative DC-link is earthed via C1//(R2+R4//D3). This makes the earth detection more as a voltage than a current monitor.

In the event of a short on the output to ground, the positive DC-link rail is grounded via the output stage (H-bridge). The negative DC-link will therefore be pushed to a negative potential and charge capacitor C1. A voltage across C1 is then converted to a 10mA current for an Opto-coupler.

### 4.8. DCCT for measuring the output current

To attain a useful feedback signal for the control loop, a suitable current transducer is required.

#### Requirements:

- Current rating: ≥340 Apk

- Bandwidth (small signal): >>40 kHz

- Tracking 54.4 A/µs

- Accuracy (DC) <<1 %

An LEM IT 400-S Ultrastab transducer is foreseen to be used as current transducer.

#### Data:

- di/dt accurately followed =  $80A/\mu s$ - 3db bandwidth = 500kHz- Accuracy =  $\leq 10 \text{ ppm}$

### 4.9. Output Filter for smooth switch transition and EMC

The output filter can be divided into two parts.

- a) Differential mode filter

- b) Common mode filter

### To s) "Differential mode filter"

The task of the differential mode filter is to:

- Reduce dv/dt on the output cable to minimize the ultra-high frequency content and EMI

- Help with the H-Bridge attain zero current switching

The differential mode filter is built up as two times 6 powder cores (6 pcs on the positive and 6 on the negative line), resulting in a total differential mode inductance of approximately 384nH. With an output cable characteristic impedance in the order of  $12\Omega$ , this results in a time constant of 32ns or a 3dB bandwidth of 5MHz.

The magnetic field change in cores is calculated to be 175mT, which gives a power loss of 6.8W or 410mW average pr. core (taking the duty cycle into account). The total power dissipation in the differential filter is 4.9W. The cores will therefore be mounted on the heat sink to ensure proper cooling.

### 0055932A2

| MPP<br>Permeability<br>(μ) | AL      |               | Coating        |                     |       |

|----------------------------|---------|---------------|----------------|---------------------|-------|

|                            | (nH/T²) | Lot<br>Number | Part<br>Number | Inductance<br>Grade | Color |

| 26                         | 32 ± 8% | XXXXXX        | 55932A2        | N/A                 | Gray  |

| Dimensions   | Unco  | ated  | Coa   | ited Limit | s   |  |

|--------------|-------|-------|-------|------------|-----|--|

| Difficusions | (mm)  | (in)  | (mm)  | (in)       |     |  |

| OD (A)       | 26.90 | 1.060 | 27.69 | 1.090      | max |  |

| ID (B)       | 14.7  | 0.580 | 14.1  | 0.555      | min |  |

| HT (C)       | 11.2  | 0.440 | 12.0  | 0.470      | max |  |

| Electrical Characteristics                   |                         |     | Physical Characteristics                                       |                               |                           |                                                       |                           |                                             |               |  |

|----------------------------------------------|-------------------------|-----|----------------------------------------------------------------|-------------------------------|---------------------------|-------------------------------------------------------|---------------------------|---------------------------------------------|---------------|--|

| Watt Loss<br>@ 100 kHz, 100mT<br>max(mW/cm³) | DC Bias<br>min (A·T/cm) |     | Voltage<br>Breakdown<br>wire to wire<br>min (V <sub>AC</sub> ) | Break<br>Strength<br>min (kg) | Window<br>Area<br>Wa(mm²) | Cross<br>Section<br>A <sub>0</sub> (mm <sup>2</sup> ) | Path<br>Length<br>Le (mm) | Volume<br>V <sub>e</sub> (mm <sup>3</sup> ) | Weight<br>(g) |  |

| 1150                                         | 80%                     | 50% | 2000                                                           | 40                            | 156                       | 65.4                                                  | 63.5                      | 4.450                                       | 31            |  |

|                                              | 95.4                    | 170 | 2000                                                           | 48                            |                           |                                                       |                           | 4,150                                       | 31            |  |

Figure 20

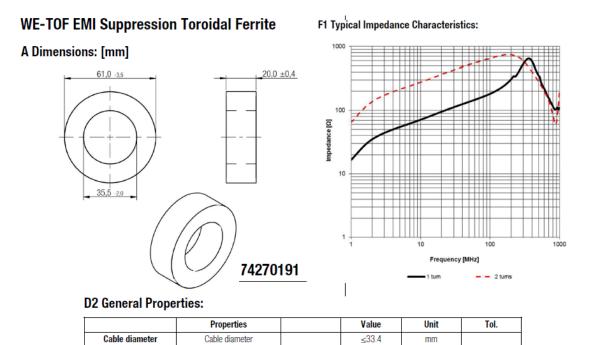

### To b) "Common mode filter"

The task of the common mode filter is to reduce EMI in the high frequency range.

The common mode filter consists of a ferrite ring placed close to the output terminals. Figure 21 shows the core type.

μį

4 W 620 620

150

AWG26

165

°C

mm

typ.

Test cable Applicable cable

Test cable Applicable cable length

Ferrite core

Ferrite core

Ferrite core

Material

Initial permeability

Curie temperature

Figure 21

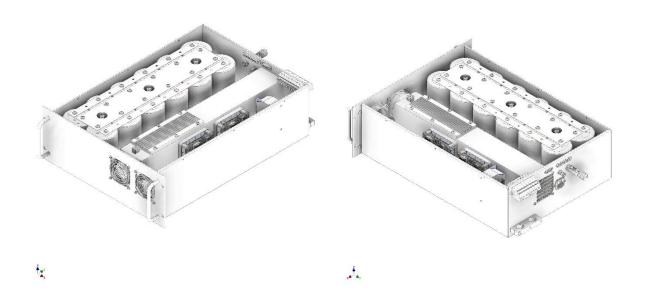

# 5. Mechanic design

The Output Converter is built in a 19" rack system having following dimension:

With: 19"Height: 4UDepth: 650mmWeight: TBD

# 5.1. Output Converter Drawing