EUROPEAN SPALLATION SOURCE

# Master Module CDR

10<sup>th</sup> February 2023 Joseph Hindmarsh, STFC Fabio Alves, NSS

#### Contents

- Overview of the Detector Readout Master Module (DRMM) Functionality and Purpose.

- FPGA Architecture, Resource usage and I/O.

- Product development.

- Readout Master Module Requirements Document.

- Summary of Local Soak and Thermal Stress Testing.

#### Before we start...

| Term   | Definition                                         |  |

|--------|----------------------------------------------------|--|

| ADC    | Analog-to-Digital Converter                        |  |

| ASIC   | Application Specific Integrated Circuit            |  |

| DMSC   | Data Management and Software Centre                |  |

| EFU    | Event Formation Unit                               |  |

| EPICS  | Experimental Physics and Industrial Control System |  |

| EVR    | Event Receiver                                     |  |

| FEBEAC | Front End Back End Assister Card                   |  |

| FEN    | Front End Node                                     |  |

| FEE    | Front End Electronics                              |  |

| FPGA   | Field Programmable Gate Array                      |  |

| MFE    | Master Front End                                   |  |

#### The Role of Detector Group Readout

- Ensure that the DAQ chain is commissionable, operable and maintainable with minimal resource requirements for the lifetime of the instrument.

- How?

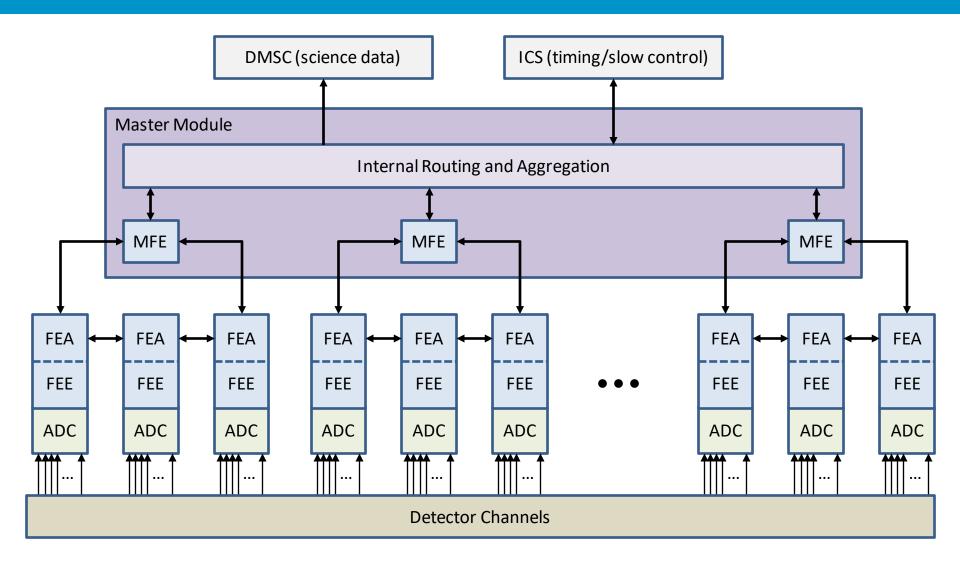

- Support instruments in the choice and development of readout front ends (digitisers and associated logic).

- Provision a generic framework for science data, slow control and timing for these front ends.

- Manage and facilitate the integration of these front ends into this generic readout framework.

#### Detector Readout Master Module (DRMM) – Requirements - ESS-4184238

#### APPLICABILITY:

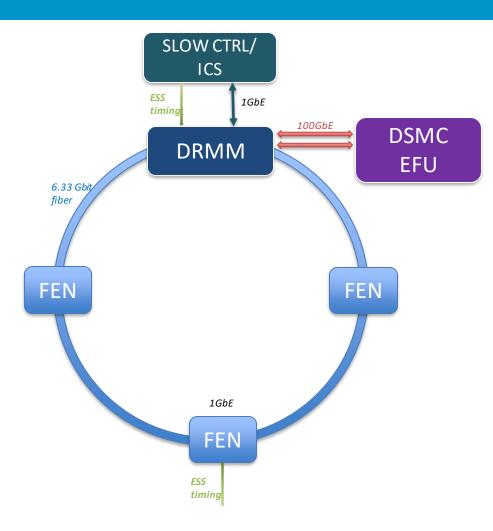

- Acquire data from the "Front End Nodes" (FENs) which interface to the front-end FPGA/ADC/detector chain.

- The connectivity between the Readout Master and the FENs is achieved through 8B/10B encoded MGT-driven (Multi-Gigabit Transceiver) optical fibres links arranged in a ring topology.

- For the slow control interface, the Readout Master instantiates a lightweight UDP stack which communicates with the EPICS IOC (Input Output Controller) using a standard Gigabit Ethernet link.

- The master module shall support an output bandwidth of 200Gb/s utilizing 2 100Gb/s Ethernet links to the EFU.

#### **ESS Readout Architecture**

Detector Readout Master Module (DRMM) – Requirements - ESS-4184238

#### Main requirements:

Logical:

- Data acquisition system common across all ESS instruments.

- Integrate ICS timing, ICS EPICS slow control and Data Egress downstream to DMSC.

- Output bandwidth 2x100Gb/s.

- Data rings to front-end: 12 bidirectional rings (24 fibers).

- Ring connection done through daughter boards interfacing with fibre via SFP connectors. Form factor:

EUROPEAN SPALLATION SOURCE

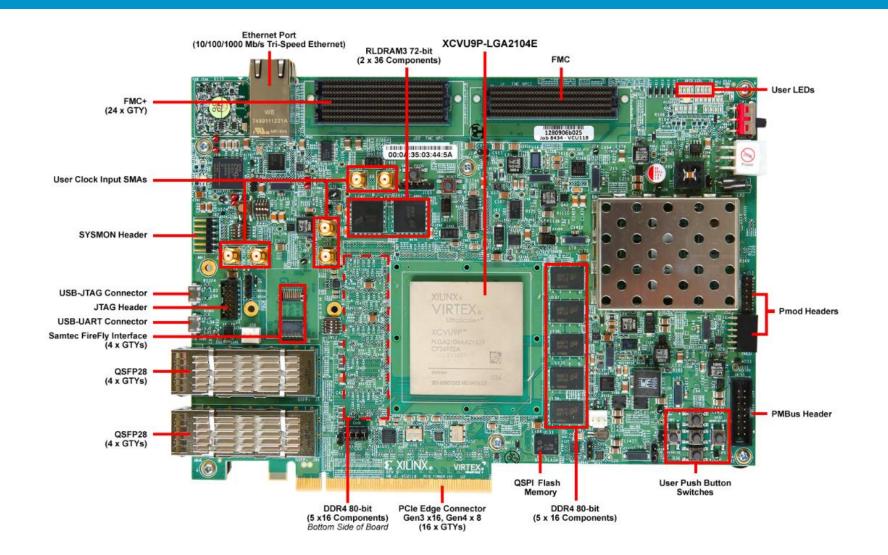

- Based around VCU118 FPGA (UltraScale+ Architecture) hardware from Xilinx.

- Fits in standard 19" rack.

- Standard Shuko power socket.

- Body of master module forms a self-contained crate, with good EMC protection.

#### **Common Detector Readout**

- The readout data is sent over Ethernet as UDP payload which can be as long as 8972 bytes long.

- Maximum transmission unit (MTU) for Ethernet of 9000 bytes.

- The connectivity between the Readout Master and the FENs is achieved through 8B/10B encoded MGT-driven (Multi-Gigabit Transceiver) optical fibres links arranged in a ring topology.

- For the slow control interface, the Readout Master instantiates a lightweight UDP stack which communicates with the EPICS IOC (Input Output Controller) using a standard Gigabit Ethernet link.

- The master module shall support an output bandwidth of 200Gb/s utilizing 2x100Gb/s Ethernet links to the EFU.

#### **FPGA** Architecture

- Virtex<sup>™</sup> UltraScale+<sup>™</sup> is a high performance FPGA, using TSMC's 16nm FinFET+ process (16FF+).

- >600 MHz operation.

- Several I/O and transceivers.

- "As the industry's most capable FPGA family, the devices are ideal for compute-intensive applications ranging from 1+Tb/s networking and machine learning."

- XCVU9P

| Device Name                                 | VU9P         |

|---------------------------------------------|--------------|

| System Logic Cells (K)                      | 2,586        |

| CLB Flip-Flops (K)                          | 2,364        |

| CLB LUTs (K)                                | 1,182        |

| Max. Dist. RAM (Mb)                         | 36.1         |

| Total Block RAM (Mb)                        | 75.9         |

| UltraRAM (Mb)                               | 270.0        |

| DSP Slices                                  | 6,840        |

| Peak INT8 DSP (TOP/s)                       | 21.3         |

| PCle <sup>®</sup> Gen3 x16                  | 6            |

| PCIe Gen3 x16/Gen4 x8 / CCIX <sup>(1)</sup> | -            |

| 150G Interlaken                             | 9            |

| 100G Ethernet w/ KR4 RS-FEC                 | 9            |

| Max. Single-Ended HP I/Os                   | 832          |

| Max. Single-Ended HD I/Os                   | 0            |

| GTY 32.75Gb/s Transceivers                  | 120          |

| GTM 58Gb/s PAM4 Transceivers                | -            |

| 100G / 50G KP4 FEC                          | -            |

| Extended <sup>(2)</sup>                     | -1 -2 -2L -3 |

| Industrial                                  | -1 -2        |

#### **FPGA Resource Usage**

| Resource | Utilisation | Maximum | %     |

|----------|-------------|---------|-------|

| LUT      | 79230       | 1182240 | 6.70  |

| LUTRAM   | 5167        | 591840  | 0.87  |

| FF       | 190018      | 2364480 | 8.04  |

| BRAM     | 221         | 2160    | 10.23 |

| DSP      | 6           | 6840    | 0.09  |

| Ю        | 59          | 832     | 7.09  |

| GT       | 29          | 52      | 55.77 |

| BUFG     | 88          | 1800    | 4.89  |

| MMCM     | 3           | 30      | 10.00 |

| PLL      | 2           | 60      | 3.33  |

Resource utilisation of Backend Master commit 9b15d30a9e944badb7118e8e1d9754fbb6127068 [6]

#### VCU118 Master IO

#### Product Development: 100 G Detector Readout Demonstrator.

# **100 G Data Generator**Second Joint BrightnESS WP4 and WP5 Jamboree 15<sup>th</sup> September 2017 Steven Alcock (DG)

## First Design

## **Final Design**

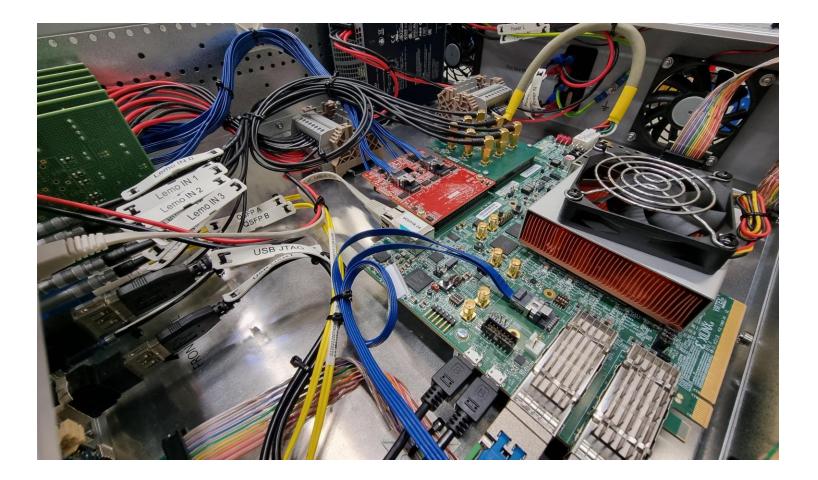

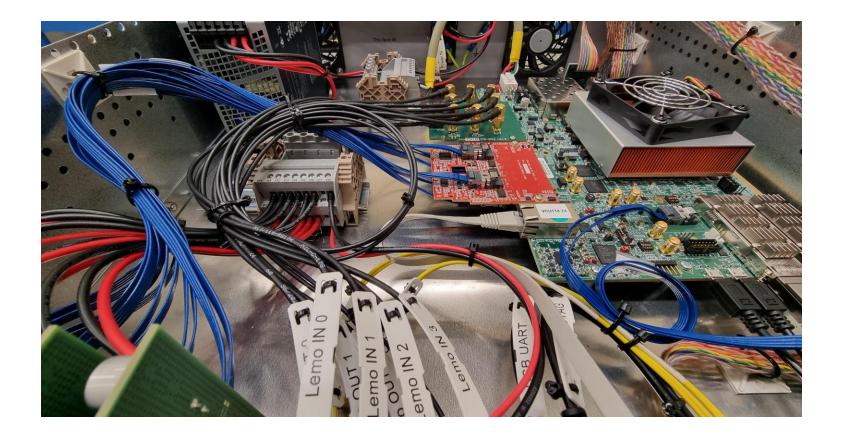

## Inside the DRMM crate – Front right corner view

#### Inside the DRMM crate –Back view

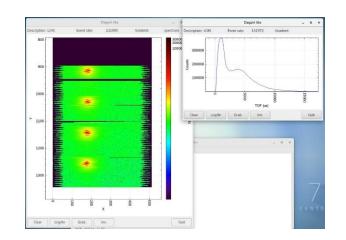

## Deployments: LOKI Beamtime (April 2021)

- Successful beamtime at ISIS was the first true endto-end test of the full DAQ chain (detector through to DMSC).

- Provides confidence that the ESS Readout System can be used for configuration, time distribution, and data readout of a real Instrument.

Steven Alcock, Detector Group, 24<sup>th</sup> January 2022 First CDR

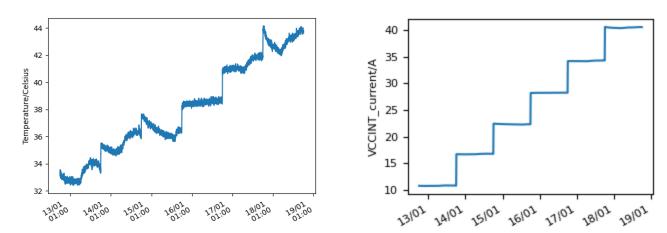

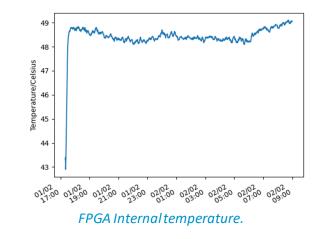

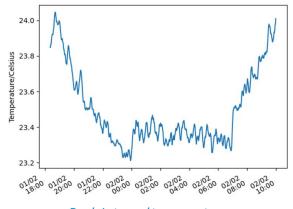

#### Local Soak Tests (January 2022)

- Custom test firmware deployed to ensure the Master Module could sustain high electrical loads over long periods of time.

- Configured the FPGA to draw increasingly large currents (far in excess of what is voltage, current and temperature measurements from the relevant on-board power regulators at 5 second intervals.

- Results showed system can operate comfortably at expected loads: full report is available.

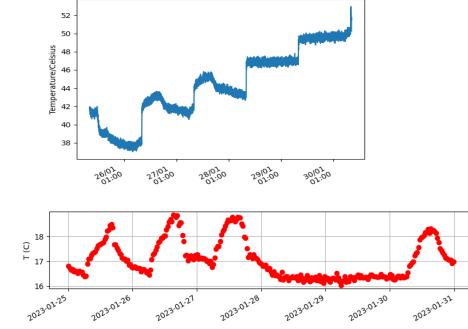

#### Local Soak Tests – Updated chassis (February 2023)

New tests were made with updated 3U/4U Verotech Caseframe chassis featuring airflow vents integrated into the top and bottom covers.

#### Local Soak Tests – Updated chassis (February 2023)

EUROPEAN SPALLATION SOURCE

- A five-day soak test similar to the prototype Master Module testing was conducted, using a closed rack with no fans installed.

- Of the 8 fans slots in the top of the rack, one was open for cables, and the other 7 were closed off. To provide additional thermal load in the rack, there was also a server and an R5560 ADC crate installed in the rack.

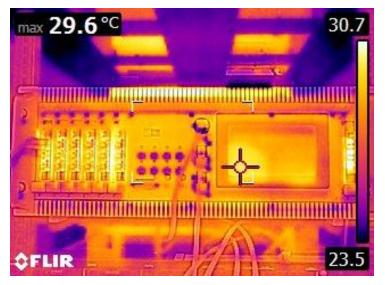

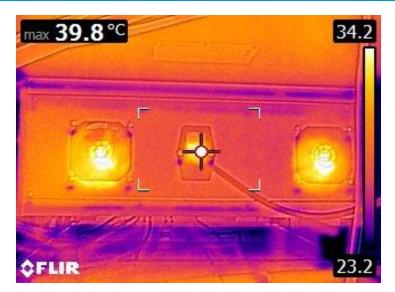

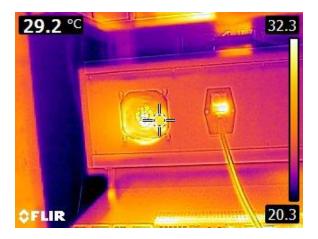

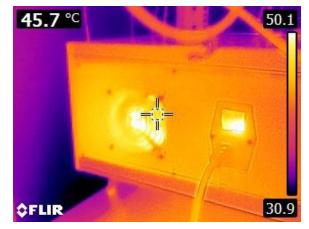

#### Soak test - Thermal Camera photos

#### Thermal stress – Ventilated Rack

RMM under test in a ventilated rack (stress test in a normal usage environment).

#### Thermal stress – Hot Rack

The ambient temperature was set to 40°C to simulate a rack fan ventilation failure.

**CELIR**

23.7

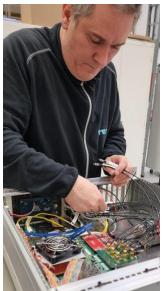

#### Readout Master Module Functionality Testing

#### • VCU118 test

- Check that the VCU118 is functional before RMM assembly

- RMM functional test

- Check that assembly has been performed correctly

|                                              |                      |                                           | project_1 -          | /home/dgr | o/project_1 | /project_1. | lpr] - Vivado | Lab Edition |

|----------------------------------------------|----------------------|-------------------------------------------|----------------------|-----------|-------------|-------------|---------------|-------------|

| Ele Edit Tools                               | Window Layout View   | w Help Q- Quick Access                    |                      |           |             |             |               |             |

| B 6 4 B                                      | n x o x ø            | Dashboard -                               |                      |           |             |             |               |             |

| -, -                                         |                      |                                           |                      |           |             |             |               |             |

| Tcl Console Mess                             | ages Serial EO Links | x Serial I/O Scans                        |                      |           |             |             |               |             |

| Q X 0 +                                      |                      |                                           |                      |           |             |             |               |             |

| Name                                         | TX                   | PX.                                       | Status               | Bits      | Err ^1      | BER         | BERT Reset    | TX Pattern  |

| S FEBEAC 1 (4)                               |                      |                                           |                      |           |             |             | Reset         | PRBS 7-bi   |

| % Link 4                                     | Ouad 126MGT X0V2     | B/TX (xcvu9p 0) Quad 126/MGT X0/28/RX (x  | CM 90 0) 6.340 Gbps  | 1.135E12  | 0E0         | 8.809E-13   | Reset         | PRBS 7-bi   |

| S Link 5                                     |                      | 9/TX (xcvu9p_0) Quad 126/MGT X0/29/RX (x  |                      | 1.141E12  | OED         | 8.764E-13   | Reset         | PRBS 7-bi   |

| % Link 6                                     |                      | IO/TX (xcvu9p 0) Quad 126/MGT X0/30/RX (x |                      | 1.141E12  | OEO         | 8.764E-13   | Reset         | PRBS 7-bi   |

| S Link 7                                     | Quad 126/MGT X0V3    | 11/TX (xcvu9p 0) Quad 126/MGT X0/31/RX (x | cwu9p 0) 6.340 Gbps  | 1.141E12  | 0E0         | 8.764E-13   | Reset         | PRBS 7-bi   |

| S FEBEAC 2 (4)                               |                      |                                           |                      |           |             |             | Reset         | PRBS 7-bi   |

| % Link 8                                     | Quad 122/MGT X0/1    | 2/TX (xcvu9p 0) Quad 122/MGT X0/12/RX (x  | cvu9p 0) 6.339 Gbps  | 1.133E12  | 0E0         | 8.827E-13   | Reset         | PRBS 7-bi   |

| S Link 9                                     | Quad 122/MGT X0/1    | 3/TX (xcvu9p 0) Quad 122/MGT X0/13/RX (x  | cvu9p_0) 6.340 Gbps  | 1.133E12  | 0E0         | 8.827E-13   | Reset         | PRBS 7-b    |

| % Link 10                                    | Quad 122/MGT X0/1    | 4/TX (xcvu9p 0) Quad 122/MGT X0Y14/RX (x  | CVUSp 0) 6.340 Gbps  | 1.133612  | 050         | 8.827E-13   | Reset         | PRBS 7-bi   |

| % Link 11                                    | Quad 122/MGT X0/1    | 5/TX (xcvu9p 0) Quad 122/MGT X0/15/RX (x  | cvu9p 0) 6.340 Gbps  | 1.133E12  | 0E0         | 8.827E-13   | Reset         | PRBS 7-bi   |

| S FEBEAC 3 (4)                               |                      |                                           |                      |           |             |             | Reset         | PRBS 7-bi   |

| % Link 12                                    | Quad 125/MGT X0V2    | A/TX (xcvu9p 0) Quad 125/MGT X0Y24/RX (x  | cvu9p 0) 6.335 Gbps  | 1.127E12  | 0E0         | 8.871E-13   | Reset         | PRBS 7-bi   |

| % Link 13                                    | Ouad 125/MGT X0V2    | 5/TX (xcvu9p 0) Quad 125/MGT X0/25/RX (x  | CVU9p 0) 6.340 Gbps  | 1.127E12  | 0E0         | 8.871E-13   | Reset         | PRBS 7-bi   |

| N Link 14                                    | Quad_125/MGT_X0V2    | 16/TX (xcvu9p_0) Quad_125/MGT_X0Y26/RX (x | cvu9p_0) 6.346 Gbps  | 1.127612  | 080         | 8.871E-13   | Reset         | PRBS 7-b    |

| % Link 15                                    | Quad_125/MGT_X0V2    | 7/TX (xcvu9p_0) Quad_125/MGT_X0V27/RX (x  | cvu9p_0) 6.340 Gbps  | 1.127E12  | 0E0         | 8.87E-13    | Reset         | PRBS 7-bi   |

| S FEBEAC 5 (4)                               |                      |                                           |                      |           |             |             | Reset         | PRBS 7-bi   |

| % Link 20                                    | Quad_120/MGT_X0V4    | VTX (xcvu9p_0) Quad_120/MGT_X0Y4/RX (xc   | (usp_0) 6.340 Gbps   | 1.12612   | 050         | 8.93E-13    | Reset         | PRBS 7-bi   |

| % Link 21                                    | Quad_120/MGT_X0/5    | (TX (xcvu9p_0) Quad_120/MGT_X0Y5/RX (xc   | (U9p_0) 6.340 Gbps   | 1.12E12   | 0E0         | 8.929E-13   | Reset         | PRBS 7-bi   |

| % Link 22                                    | Quad_120/MGT_X0V6    | (TX (xcvu9p_0) Quad_120/MGT_X0Y6/RX (xc   | (USp_0) 6.340 Gbps   | 1.12612   | 050         | 8.929E-13   | Reset         | PRBS 7-bi   |

| N Link 23                                    | Quad_120/MGT_X0Y7    | TX (xcvu9p_0) Quad_120/MGT_X0Y7/RX (xc    | (U9p_0) 6.340 Gbps   | 1.12E12   | 0E0         | 8.929E-13   | Reset         | PRBS 7-bi   |

| S FEBEAC 6 (4)                               |                      |                                           |                      |           |             |             | Reset         | PRBS 7-bi   |

| % Link 24                                    | Quad_233/MGT_X115    | i6/TX (xcvu9p_0) Quad_233/MGT_X1V56/RX (x | cvu9p_0) 1.761 Gbps  | 3.092611  | OEO         | 3.234E-12   | Reset         | PRBS 7-bi   |

| N Link 25                                    | Quad_233/MGT_X115    | 7/TX (xcvu9p_0) Quad_233/MGT_X1V57/RX (x  | cvu9p_0) 1.761 Gbps  | 3.092E11  | 0E0         | 3.234E-12   | Reset         | PRBS 7-bi   |

| N Link 26                                    | Quad_233/MGT_X115    | 8/TX (xcvu9p_0) Quad_233/MGT_X1V58/RX (x  | cvu9p_0) 1.761 Gbps  | 3.092E11  | 0E0         | 3.234E-12   | Reset         | PRBS 7-bi   |

| % Link 27                                    | Quad_233/MGT_X1V5    | 9/TX (xcvu9p_0) Quad_233/MGT_X1V59/RX (x  | cvu9p_0) 1.761 Gbps  | 3.092E11  | OEO         | 3.234E-12   | Reset         | PRBS 7-bi   |

| \$\low \left(\mathbf{Q}\) \left(\mathbf{A}\) |                      |                                           |                      |           |             |             | Reset         | PRBS 7-bi   |

| N Link 28                                    | Quad_232/MGT_X115    | 2/TX (xcvu9p_0) Quad_232/MGT_X1V52/RX (x  | cvu9p_0) 28.126 Gbps | 4.904E12  | 0E0         | 2.039E-13   | Reset         | PRBS 7-bi   |

| N Link 29                                    | Quad_232/MGT_X115    | 3/TX (xcvu9p_0) Quad_232/MGT_X1Y53/RX (x  | CVU90 0) 28.126 Gbps | 4.904E12  | OED         | 2.039E-13   | Reset         | PRBS 7-bi   |

#### Readout Master Module Functionality Testing

#### • IBERT

- Integrated Bit Error Rate Test

- Xilinx IP core

- Test Multi-Gigabit Transceivers

- Used to test

- Ring transceivers (24x6.34Gbps)

- 100GbE transcievers (8x25.78Gbps)

- Timing system (Embedded EVR) transceiver (1x1.76Gbps)

- Also tests clock chip programming

|                   |                         |                                       | project_1 -        | [/home/dgr | o/project_1 | /project_1. | lpr] - Vivado L | ab Editio |

|-------------------|-------------------------|---------------------------------------|--------------------|------------|-------------|-------------|-----------------|-----------|

| Ele Edit Tools    | Window Layout View      | Help Q+ Quick Access                  |                    |            |             |             |                 |           |

|                   | XOXØX                   |                                       |                    |            |             |             |                 |           |

|                   |                         |                                       |                    |            |             |             |                 |           |

| Tcl Console Messa | ges Serial I/O Links ×  | Serial I/O Scans                      |                    |            |             |             |                 |           |

| Q X 0 +           |                         |                                       |                    |            |             |             |                 |           |

| Name              | TX                      | RX                                    | Status             | Bits       | Err. ^1     | BER         | BERT Reset      | TX Patte  |

| ✓ ⊗ FEBEAC 1 (4)  |                         |                                       |                    |            |             |             | Reset           | PRBS 7-   |

| % Link 4          | Quad 126/MGT X0V28/TX   | (xcvu9p_0) Quad 126/MGT_X0Y28/RX (xcv | ugo 0) 6.340 Gbps  | 1.135E12   | OEO         | 8.809E-13   | Reset           | PRBS 74   |

| % Link 5          |                         | (xcvu9p_0) Quad 126/MGT X0Y29/RX (xcv |                    | 1.141E12   | 0E0         | 8.764E-13   | Reset           | PRBS 7-4  |

| % Link 6          |                         | (xcvu9p_0) Quad 126/MGT_X0Y30/RX (xcv |                    | 1.141E12   | OEO         | 8.764E-13   | Reset           | PRBS 7-   |

| % Link 7          |                         | (xcvu9p_0) Quad 126/MGT X0Y31/RX (xcv |                    | 1.141E12   | 0E0         | 8.764E-13   | Reset           | PRBS 7-4  |

| S FEBEAC 2 (4)    |                         |                                       |                    |            |             |             | Reset           | PRBS 7-   |

| % Link 8          | Quad 122/MGT X0Y12/TX   | (xcvu9p 0) Quad 122/MGT X0Y12/RX (xcv | u9p 0) 6.339 Gbps  | 1.133E12   | 0E0         | 8.827E-13   | Reset           | PRBS 7-8  |

| % Link 9          | Quad 122/MGT_X0Y13/TX   | (xcvu9p_0) Quad 122/MGT_X0Y13/RX (xcv | u9p_0) 6.340 Gbps  | 1.133E12   | OEO         | 8.827E-13   | Reset           | PRBS 74   |

| % Link 10         | Quad 122/MGT X0Y14/TX   | (xcvu9p 0) Quad 122/MGT X0Y14/RX (xcv | u9p 0) 6.340 Gbps  | 1.133E12   | 0E0         | 8.827E-13   | Reset           | PRBS 74   |

| % Link 11         | Quad_122/MGT_X0Y15/TX   | (xcvu9p_0) Quad_122/MGT_X0Y15/RX (xcv | u9p_0) 6.340 Gbps  | 1.133E12   | 0E0         | 8.827E-13   | Reset           | PRBS 74   |

| ✓ S FEBEAC 3 (4)  |                         |                                       |                    |            |             |             | Reset           | PRBS 74   |

| % Link 12         | Quad_125/MGT_X0V24/TX   | (xcvu9p_0) Quad_125/MGT_X0Y24/RX (xcv | u9p_0) 6.335 Gbps  | 1.127E12   | 0E0         | 8.871E-13   | Reset           | PRBS 74   |

| % Link 13         | Quad_125/MGT_X0Y25/TX   | (xcvu9p_0) Quad_125/MGT_X0Y25/RX (xcv | u9p_0) 6.340 Gbps  | 1.127E12   | 0E0         | 8.871E-13   | Reset           | PRBS 74   |

| % Link 14         | Quad_125/MGT_X0V26/TX   | (xcvu9p_0) Quad_125/MGT_X0Y26/RX (xcv | u9p_0) 6.346 Gbps  | 1.127E12   | 0E0         | 8.871E-13   | Reset           | PRBS 7-   |

| % Link 15         | Quad_125/MGT_X0Y27/TX   | (xcvu9p_0) Quad_125/MGT_X0V27/RX (xcv | u9p_0) 6.340 Gbps  | 1.127E12   | 0E0         | 8.87E-13    | Reset           | PRBS 74   |

| See FEBEAC 5 (4)  |                         |                                       |                    |            |             |             | Reset           | PRBS 74   |

| % Link 20         | Quad_120/MGT_X0Y4/TX 0  | (cvu9p_0) Quad_120/MGT_X0Y4/RX (xcvu  | (9p_0) 6.340 Gbps  | 1.12E12    | 0E0         | 8.93E-13    | Reset           | PRBS 7-8  |

| % Link 21         | Quad_120/MGT_X0Y5/TX 0  | (cvu9p_0) Quad_120/MGT_X0Y5/RX (xcvu  | 9p_0) 6.340 Gbps   | 1.12E12    | 0E0         | 8.929E-13   | Reset           | PRBS 7-4  |

| % Link 22         | Quad_120/MGT_X0Y6/TX () | (cvu9p_0) Quad_120/MGT_X0Y6/RX (xcvu  | 9p_0) 6.340 Gbps   | 1.12E12    | 0E0         | 8.929E-13   | Reset           | PRBS 7-   |

| % Link 23         | Quad_120/MGT_X0Y7/TX 0  | (cvu9p_0) Quad_120/MGT_X0Y7/RX (xcvu  | 9p_0) 6.340 Gbps   | 1.12E12    | 0E0         | 8.929E-13   | Reset           | PRBS 74   |

| S FEBEAC 6 (4)    |                         |                                       |                    |            |             |             | Reset           | PRBS 74   |

| % Link 24         | Quad_233/MGT_X1Y56/TX   | (xcvu9p_0) Quad_233/MGT_X1Y56/RX (xcv | u9p_0) 1.761 Gbps  | 3.092E11   | 0E0         | 3.234E-12   | Reset           | PRBS 7-   |

| % Link 25         | Quad_233/MGT_X1Y57/TX   | (xcvu9p_0) Quad_233/MGT_X1Y57/RX (xcv | u9p_0) 1.761 Gbps  | 3.092E11   | 0E0         | 3.234E-12   | Reset           | PRBS 7-   |

| % Link 26         | Quad_233/MGT_X1Y58/TX   | (xcvu9p_0) Quad_233/MGT_X1Y58/RX (xcv | u9p_0) 1.761 Gbps  | 3.092E11   | 0E0         | 3.234E-12   | Reset           | PRBS 7-   |

| % Link 27         | Quad_233/MGT_X1Y59/TX   | (xcvu9p_0) Quad_233/MGT_X1Y59/RX (xcv | u9p_0) 1.761 Gbps  | 3.092E11   | 0E0         | 3.234E-12   | Reset           | PRBS 7-   |

| V % QSFP 0 (4)    |                         |                                       |                    |            |             |             | Reset           | PRBS 74   |

| % Link 28         |                         | (xcvu9p_0) Quad_232/MGT_X1Y52/RX (xcv |                    | 4.904E12   | 0E0         | 2.039E-13   | Reset           | PRBS 7-8  |

| % Link 29         | Quad_232/MGT_X1Y53/TX   | (xcvu9p_0) Quad_232/MGT_X1Y53/RX (xcv | u9p_0) 28.126 Gbps | 4.904E12   | 0E0         | 2.039E-13   | Reset           | PRBS 7-4  |

#### Readout Master Module Functionality Testing

- Other interface tests

- JTAG

- UART

- 1G Ethernet

- Touchscreen

- LEMO

- HFBR

| Square,OFF,51 | Sine,OFF,500                       |

|---------------|------------------------------------|

| Frequency     | 25.000,000,00MHz                   |

| Amplitude     | 3.300 Vpp                          |

| Offset        | 1.650 V                            |

| Phase         | 0.000°                             |

| Duty Cycle    | 50.00%                             |

|               |                                    |

| CH1 Output    |                                    |

|               | Output Range Polarity Voltage Dual |

| Off De        | Load Auto Normal Limits Channel    |

| Device DNA:                | VCCINT:   |

|----------------------------|-----------|

| 0×40020000                 | 3.750 W   |

| 0x01178A25                 | VCC1V8:   |

| 0x3C710245                 | 1.875 W   |

| Git Hash:                  | VADJ:     |

| Охааааааа                  | 0.075 W   |

| 0×BBBBBBBB                 | VCC1V2:   |

| 0xCCCCCCC                  | 0.375 W   |

| Bitstream Generation Time: | MGTAVCC:  |

| 00-00-00 00:00 00          | 1.975 W   |

| Up Time:                   | MGTAVTT:  |

| 00 00:00:26                | 14.10 W   |

| Current FPGA Temperature:  | VINTBRAM: |

| 23.6 degrees C             | 0.200 W   |

| Highest FPGA Temperature:  |           |

| 32.0 degrees C             |           |

EUROPEAN SPALLATION SOURCE

# Questions

#### Xilinx Product Longevity

#### **Product Longevity**

A product lifecycle is typically defined by four main phases: introduction, growth, maturity, and decline. Xilinx designs products and creates the supporting supply chain with the clear intent to support a minimum **15+ year lifecycle\***, starting from first production release. Xilinx parts are used extensively in numerous applications that require a long operational lifetime, and therefore, Xilinx makes a strong commitment to product longevity. With this commitment, although the minimum lifecycle is 15 years, customers will see that the majority of families will be supported much longer. The longevity of

Xilinx products is longer than ASSPs, ASICs, and other major FPGA suppliers. In the case of a last time buy, Xilinx does follow the JEDEC standard.

https://www.xilinx.com/support/quality/support.html#productLongevity